ANZINE : CAE 기술 매거진

이전 ANZINE Home Tech-Insight

▶ 67호 : SIwave를 이용한 Package에 대한 EM MTTF 해석

- 김미정 매니저

- 태성에스엔이

- mj.kim@tsne.co.kr

SIwave를 이용한 Package에 대한 EM MTTF 해석

Ansys SIwave에서는 반도체 디바이스의 신뢰성 분석을 위한 EM MTTF Simulation 기능을 제공한다. 이번 호에서는 Electromigration에 대한 간단한 정의와 SIwave를 이용한 package에 대한 EM MTTF 해석 방법에 대해 알아본다.

Introduction

도체에 전압이 가해지면 전자들이 이동하면서 금속 이온을 이동시키는 현상이 나타난다. 이 현상을 Electromigration이라고 하며 주로 금속 선로에서 발생한다. 이 Electromigration으로 인해 Open 또는 Short와 같은 물질의 구조적 변화가 발생하여 반도체 디바이스의 전기적 성능 저하나 고장이 발생할 수 있다. 이 Electromigration은 전류 밀도가 클수록 발생하기 쉬운 특성을 가지고 있다. Package의 경우 좁은 영역에 Interconnect의 밀도가 높기 때문에 Electromigration 분석을 통해 Package 설계 단계에서 전류 밀도를 제한하고 반도체 디바이스의 신뢰성을 높여야 한다.

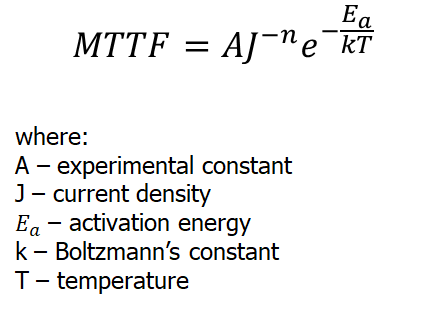

SIwave에서는 Electromigration으로 인해 반도체가 고장에 이르는 평균 시간(Mean Time to Failure)을 예측할 수 있게 EM MTTF Simulation 기능을 제공한다. 이 MTTF는 [식 1]의 Black의 방정식으로 계산할 수 있으며 시간 단위로 표현된다. MTTF가 높을수록 고장이 적게 발생하는 안정적인 디바이스라고 판단할 수 있다. SIwave의 EM MTTF Simulation 기능은 DC IR Drop Simulation 분석 결과인 전류 밀도를 바탕으로 Black의 방정식을 계산하여 MTTF를 예측한다.

[식 1] Black의 방정식

SIwave의 EM MTTF Simulation

EM MTTF Simulation을 진행하기 위해서는 반드시 먼저 DC IR Drop Simulation을 진행해야 한다. DC IR Drop Simulation 결과 중 하나인 전류 밀도 결과를 이용하여 Black의 방정식을 계산하기 때문이다.

SIwave의 DC IR Drop Simulation은 Icepak과 연계 해석을 지원하므로 연계 해석을 통해 Joule Heating을 고려한 열해석 후, 온도 맵 데이터를 EM MTTF Simulation에 반영할 수 있다.

1. Package 디자인 불러오기

첫 번째 단계로 ECAD에서 작성한 Package 디자인을 SIwave에 불러와야 한다.

2. Model 검증

두 번째 단계로 불러온 데이터들에 대해 검증을 진행해야 한다. 정확한 Simulation을 위해 Stackup이 올바르게 설정되어 있는지, 불러들인 Padstack에는 문제가 없는지 그리고 Non-signal Net은 Power/GND net으로 분류가 되었는지 확인해야 한다.

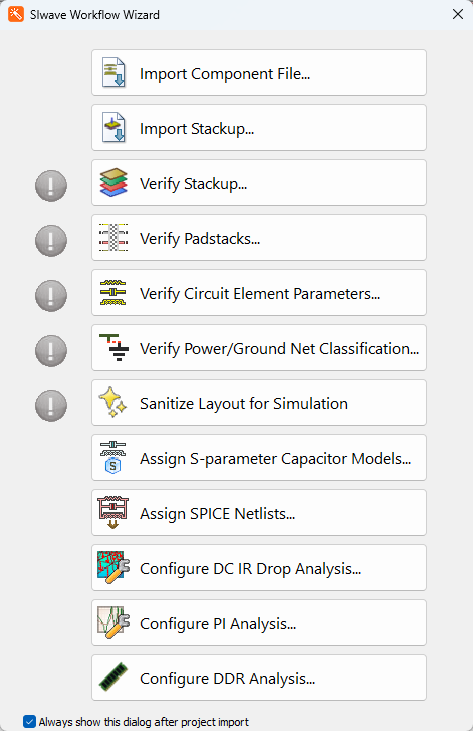

이러한 과정을 메뉴를 이용해서 진행해도 되지만 [그림 1]과 같이 SIwave에서 제공되는 Workflow Wizard를 이용해서 단계별로 진행할 수 있다.

[그림 1] SIwave의 Workflow Wizard

3. Solderball 및 Bondwire 설정

BGA Package에 대해 Solderball 속성을 설정한다. Solderball이 얹힐 Padstack 별로 Solderball 형태, 사이즈, 재질 및 배치 방향을 설정할 수 있다. 형태는 원통형, 밑면이 좁은 원통형 그리고 위/아랫면이 좁은 원통형을 지원한다. Solderball 설정을 완료하면 Padstack 위/아래에 3D 형태의 Solderball이 생성된다.

Wirebonding이 사용된 경우 Bondwire 설정도 진행한다. [그림 2]와 같이 SIwave에서 제공하는 Bondwire Model Editor에 값을 입력하여 Bondwire를 쉽게 생성할 수 있다. Bondwire 모델로 4 point, 5 point의 JEDEC 표준 모델을 지원한다. 그리고 사용자가 원하는 형태의 Bondwire도 생성할 수 있다.

[그림 2] SIwave의 Solderball Properties 창(왼쪽) 및 Bondwire Model Editor 창(오른쪽)

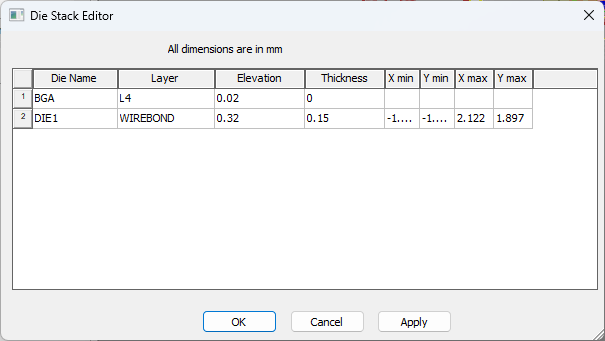

4. IC Die 두께 설정

도면상에 Die가 포함된 경우에 [그림 3]의 Die Stack Editor에 IC Die의 두께를 설정한다. Wire-bond Package의 경우 Die의 두께에 따라 Bonding 높이가 달라지기 때문에 정확한 두께를 설정해야 한다.

[그림 3] SIwave의 Die Stack Editor

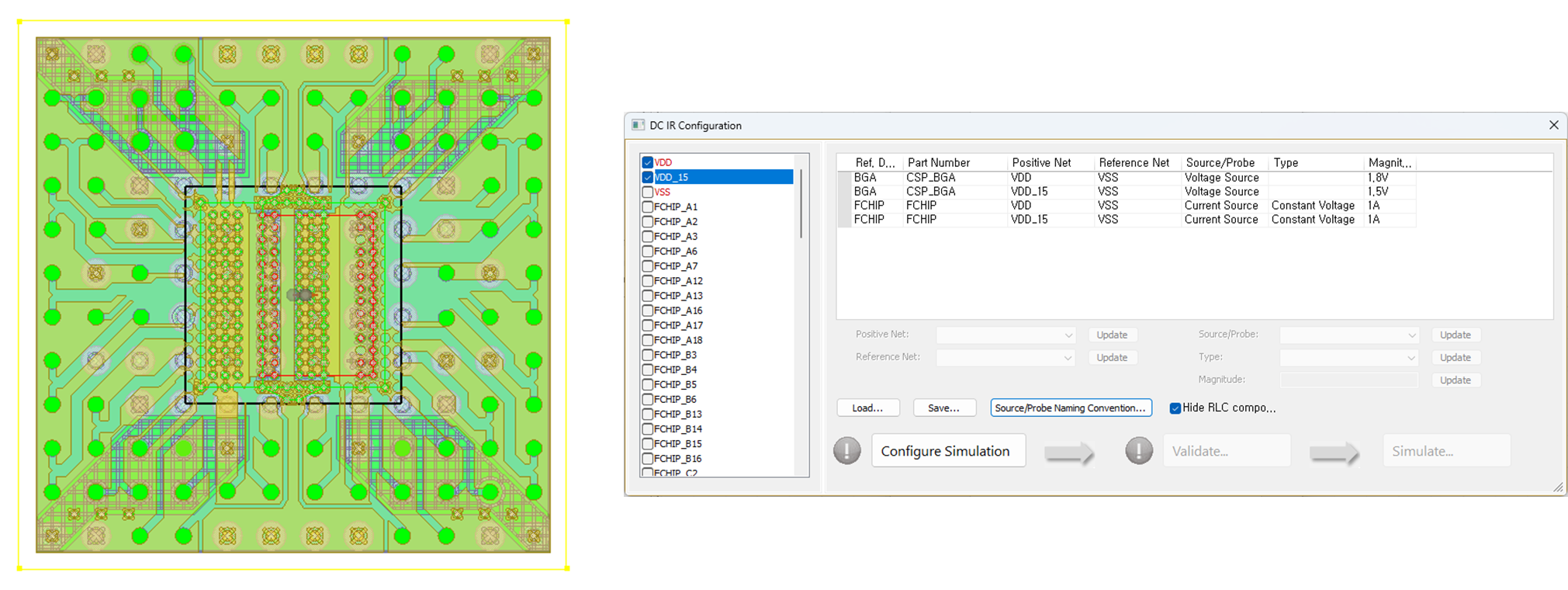

5. DC IR Drop Simulation 설정

세 번째 단계로 Voltage Source, Current Source를 정의해야 한다. [그림 4]의 DC IR Configuration 창에서 Package substrate의 pin에 voltage source와 공급 전원 값을 설정한다. Die의 pin에는 Current Source와 소모 전류를 설정한다. Configure Simulation을 실행하면 이 설정에 따라 자동으로 Pin Group을 생성되고 Voltage Source, Current Source가 설정된다. 다음 Validate를 실행하여 Open, Short 등 디자인에 오류가 있는지 검사한다. 에러가 있는 경우에는 오류 수정을 진행한다.

[그림 4] 해석할 Package 디자인과 SIwave의 DC IR Configuration 창

6. DC IR Drop Simulation 실행

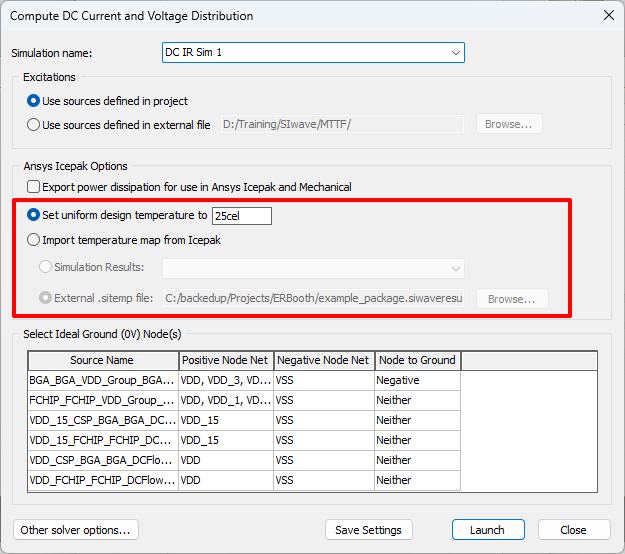

다음으로 DC IR Drop Simulation을 실행한다. [그림 5]의 Compute DC Current and Voltage Distribution 창에서 디자인 온도를 설정하거나 Icepak 열해석 결과인 온도 맵 데이터를 불러와서 온도에 따른 전도율을 반영하여 해석할 수 있다. 설정이 완료되면 Simulation을 실행한다.

[그림 5] SIwave의 Compute DC Current and Voltage Distribution 창

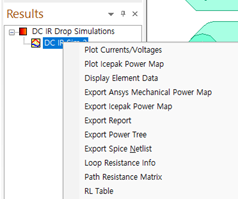

Simulation이 끝나면 [그림 6]의 결과 메뉴를 이용하여 Via 전류/전류 밀도/전압 분포/전력 밀도에 대한 Plot, Path Resistance 값, Loop Resistance 값 등 다양한 Simulation 결과를 확인할 수 있다.

[그림 6] Simulation 결과 데이터 출력 메뉴

7. EM MTTF Simulation 실행

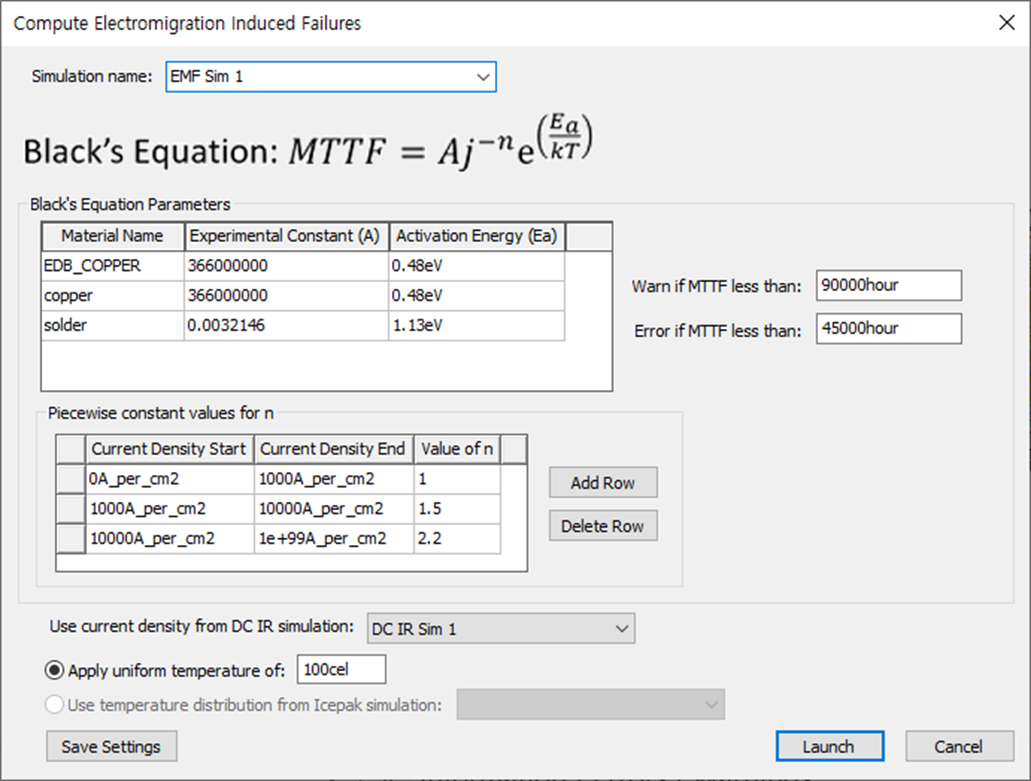

Black의 방정식을 계산하기 위해 [그림 7]의 EM MTTF Simulation 창에 Black의 방정식의 Parameter를 설정한다. 온도의 경우 일정한 Board 온도를 입력하거나 Icepak 열해석 결과(온도 분포)를 반영할 수도 있다. 마지막으로 MTTF에 대한 Warning/Error 기준을 설정한 후 Simulation을 실행한다.

[그림 7] SIwave의 EM MTTF Simulation 창

해석 결과

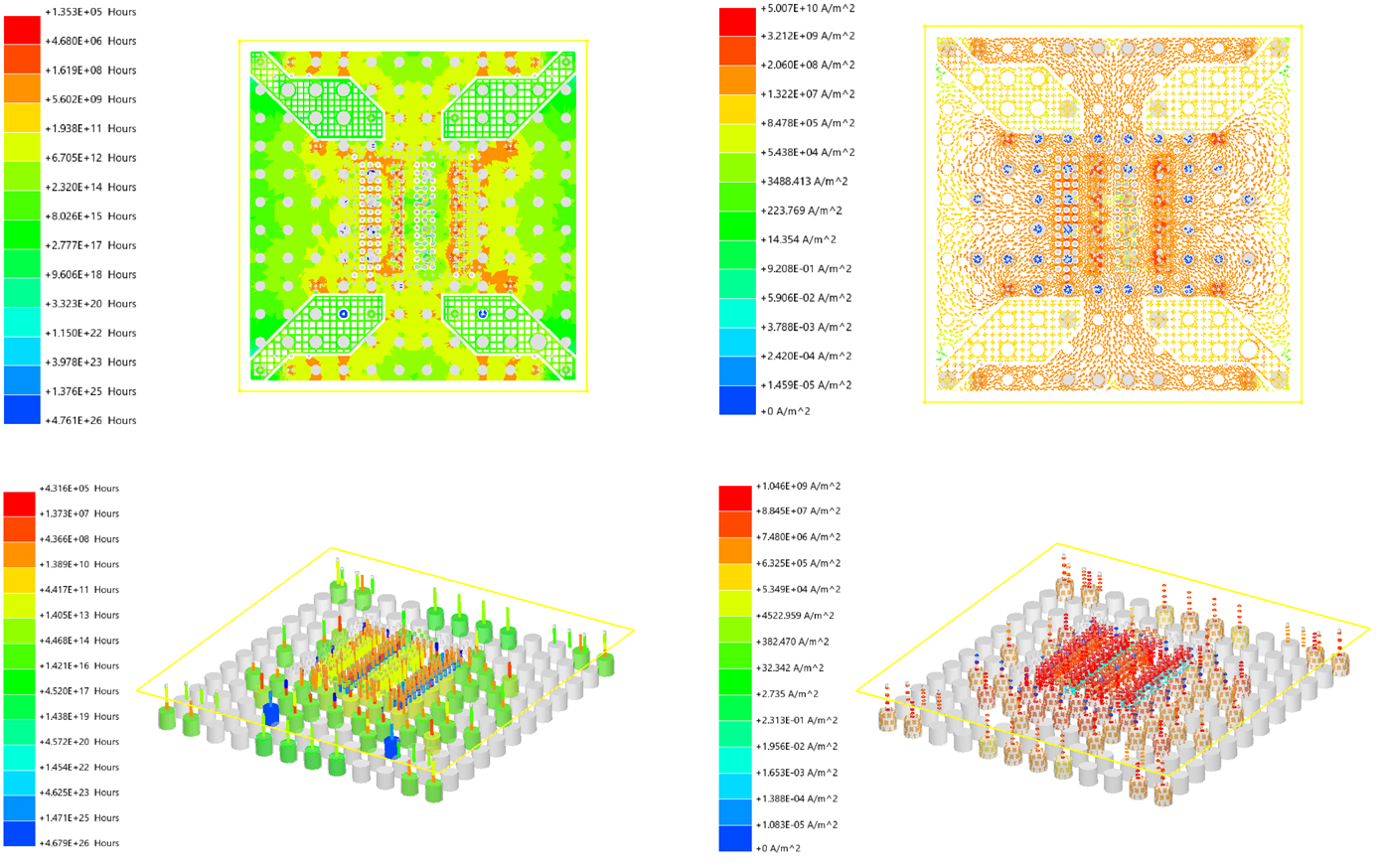

[그림 8]과 같이 EM MTTF 결과로 MTTF Plot과 Violation Plot을 확인할 수 있다. Copper에 대한 MTTF뿐 아니라 Via, Solderball에 대한 MTTF 분석 결과도 확인할 수 있어 MTTF 기준을 맞추기 위한 Padstack 및 Solderball을 설계할 수 있다. DC IR Drop Simulation 결과인 전류 밀도 Plot과 함께 확인하면서 MTTF 기준에 만족하지 못한 영역을 개선해야 한다.

[그림 8] MTTF Plot(왼쪽) 및 Current Density Plot(오른쪽)

맺음말

Package의 신뢰성을 확보하기 위해 SIwave에서 DC IR Drop Simulation 진행 후 전류 밀도 결과를 바탕으로 EM MTTF 분석하는 방법에 대해서 살펴보았다. 이렇게 SIwave, 한 솔루션을 이용하여 전원 무결성(Power Integrity) 뿐 아니라 Package의 신뢰성도 확보할 수 있다.

㈜태성에스엔이

㈜태성에스엔이