ANZINE : CAE 기술 매거진

이전 ANZINE Home Tech-Insight

Ansys HFSS 3D Layout을 이용한 HBM3의 High Speed Interposer 해석 방법

- 양철승 매니저

- 태성에스엔이

- csyang@tsne.co.kr

Ansys HFSS 3D Layout을 이용한 HBM의 High Speed Interposer 해석 방법

Introduction

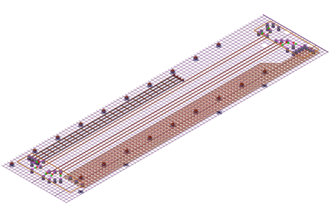

고성능 컴퓨팅 및 데이터 집약적인 애플리케이션의 급속한 발전으로 인해 메모리 기술 역시 빠르게 진화하고 있습니다. 이러한 흐름 속에서 HBM(High Bandwidth Memory)은 최신의 고성능 메모리 솔루션으로 주목받고 있습니다. HBM은 높은 대역폭과 에너지 효율성을 제공하며, 이를 통해 그래픽 처리, 인공지능, 데이터 센터와 같은 분야에서 탁월한 성능을 발휘할 수 있습니다. HBM의 성능을 극대화하기 위해서는 고속 인터포저(Interposer)의 역할이 매우 중요합니다. 본 글에서는 Ansys HFSS 3D Layout을 이용하여HBM 동작을 위한 High Speed Interposer 해석 방법에 대해 심도 있게 살펴보겠습니다. 그림 1은 인터포저 예제 그림입니다.

[그림1] Interposer 예제 사진

인터포저 해석을 위해서는 IC Mode를 사용해야 합니다.

HFSS IC Mode 소개

IC 및 인터포저 시뮬레이션 분석을 해결하기 위해 HFSS는 다음과 같은 특성을 가진 IC 모드를 도입했습니다.

- 다층 평면 구조에 대한 고려 사항 : IC는 일반적으로 다층 구조이며 IC Mode는 이러한 다층 구조를 보다 정확하게 시뮬레이션하고 분석하는데 도움이 되는 3D 레이아웃 프레임워크 운영 환경을 기반으로 합니다.

- GDSII 지원 : IC 설계에서 부품 규모는 나노미터에서 마이크론 수준(nm-um)까지 다양하며 설계 파일은 일반적으로 GDS 형식으로 존재합니다. 따라서 IC Mode는 GDS 형식 파일 가져오기가 지원됩니다.

- 암호화 모델 지원 : 제조 IC에서는 웨이퍼 공장에서 상세한 공정 기술 문서를 제공해야 합니다. 이러한 문서에는 대량의 레이어 적층 정보가 포함되어 있는 경우가 많으며, 지적 재산권이 관련되어 있으므로 이러한 기술 문서는 암호화되는 경우가 많습니다. 따라서 IC Mode는 암호화된 공정 기술 문서의 가져오기가 지원되어야 합니다.

- 많은 수의 포트 지원 : IC 설계에는 수십만 개의 포트가 있을 수 있으므로 IC Mode는 보다 편리한 포트 설정 방법을 제공합니다.

- 레이아웃 단순화 : IC 설계의 레이아웃 규모가 매우 작기 때문에 연결에는 비아 어레이가 자주 사용됩니다. 이 경우 IC Mode의 복잡한 레이아웃을 단순화하는 방법에는 여러 가지가 있습니다.

- 복잡한 인터포저 구조의 가속 계산 : 복잡한 인터포저 구조를 가진 설계의 경우 IC Mode는 다양한 가속 처리 기능을 제공하여 해석을 더 빠르게 완료합니다.

- 모델 추출 유연성 : 다양한 요구 사항(예: SI, PI 또는 RF 분석)에 따라 IC Mode 그래프는 다양한 설계 및 분석 요구 사항을 충족하기 위해 다양한 유형의 모델 추출을 지원하는 다양한 솔버를 제공합니다.

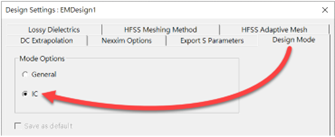

요약하면 HFSS의 IC 모드는 최신 고속, 고주파 전자 설계의 요구 사항에 맞게 설계되었으며 이러한 설계의 특정 과제를 충족할 수 있는 다양한 기능을 제공합니다. 그림2는 IC mode 설정 방법입니다. 그림3은 IC mode 및 General mode 에서의 솔버 및 아이콘 차이입니다.

[그림2] HFSS 3D Layout 에서 IC Mode 설정 화면

[그림3] General Mode VS IC Mode 솔버, 아이콘 차이

Interposer 해석 프로세스

1. GDSII 가져오기

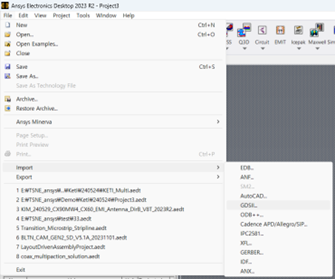

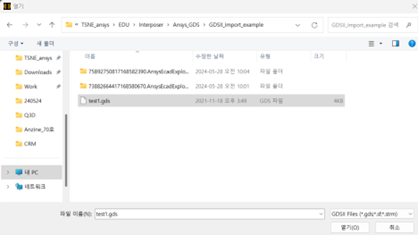

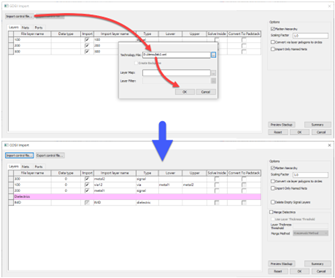

아래 그림은 Ansys Electronics Desktop 소프트웨어에서 GDSII 파일을 가져오는 프로세스를 보여줍니다. 구체적인 단계는 다음과 같습니다. 그림4는 GDS 파일 import 방법입니다.

[그림4] GDSII 가져오기

1) 소프트웨어 열기 : 먼저 Ansys Electronics Desktop을 엽니다.

2) 가져오기 옵션 선택 : 소프트웨어 상단 메뉴 표시줄에서 File > Import를 클릭합니다.

3) 파일 형식 선택 : 드롭다운 메뉴에서 GDSII...파일 형식을 선택합니다.

4) 파일 찾아보기 및 선택 :

- 나타나는 파일 선택 대화 상자에서 GDSII 파일이 포함된 디렉터리를 찾습니다.

- 가져오려는 GDSII 파일을 선택합니다.(예: example.gds)

5) GDSII 가져오기 창 열기 : 파일을 선택한 후 열기(O)버튼을 클릭하여 GDSII 가져오기 창을 엽니다.

2. 제어 파일 가져오기

GDSII Import 창에서 "Import control file..." 버튼을 클릭하여 제어 파일 .xml을 가져옵니다. 그림5는 xml 파일 가져오기 메뉴 사진입니다.

[그림5] .xml 가져오기

다음과 같은 수치 변화를 관찰할 수 있습니다.

1) 레이어(Layer) 순서 재배열 : 그림5의 100, 200, 300 3개의 레이어가 순서대로 나열되어 있습니다. 그림5의 레벨 300, 100, 200의 순서가 XML의 Elevation 정의에 따라 재배열되었습니다.

2) 레이어 이름 가져오기 :

- 그림5의 "Import layer name" 열에 "File layer name" 열과 동일한 내용이 있음을 보여줍니다.

- 그림5의 레벨 300, 100 및 200이 각각 "metal2", "via1" 및 "metal1"에 해당함을 보여줍니다. 이는 XML이 GDSII 파일의 레벨을 특정 레이어 이름에 매핑했음을 보여줍니다.

3) 유형 변경 : 100번 레이어를 관찰하면 유형이 via로 변경됩니다. 그리고 Lower(하한) 및 Upper(상한)는 각각 "metal1" 및 "metal2"에 해당합니다. 층 100(via12)이 금속 1 층과 금속 2 층을 연결하는 관통 구멍임을 나타냅니다. 이 두 필드는 비아의 연결 상한 및 하한을 정의합니다.

4) 유전체 레이어 추가 : 가져오기 인터페이스 아래에 "유전체"라는 새 섹션이 추가되고 "IMD"라는 유전체 레이어가 구체적으로 나열되는 것을 확인했습니다.

3. Via Grouping 및 Dielectric Merging

전자기 시뮬레이션에 GDSII 파일을 사용할 때 다음 문제에 특별한 주의가 필요합니다.

1) 작은 형상의 큰 존재 : 시뮬레이션에서 수천 개의 작은 형상을 고려해야 하며, 이는 솔버 성능에 부담을 주고 메쉬 생성의 복잡성을 증가시킵니다.

2) 인접 레이어의 형상 미스매칭 : 서로 다른 레이어의 형상 미스매칭은 이러한 차이를 처리하기 위해 추가 계산이 필요할 수 있습니다.

3) 매우 얇고 수많은 유전체 레이어 : 이러한 레이어를 결합하거나 단순화하여 모델 복잡성을 줄여 시뮬레이션에 필요한 시간과 계산 리소스를 절약해야 할 수 있습니다.

Via Grouping

웨이퍼 제조 공정에서는 수천 개의 작은 비아(via)를 사용하여 신호 레이어 간의 연결을 설정하는 것이 일반적입니다. Ansys Electronics Desktop Layout Editor에서 이러한 비아는 일반적으로 정사각형 프리미티브로 표시됩니다. 이 표현은 제조에 중요하지만 시뮬레이션의 경우 부적절한 메쉬 밀도를 도입하여 계산 복잡성을 증가시킬 수 있습니다.

Via Grouping 옵션을 사용하면 이러한 정사각형 프리미티브를 그룹화하고 단일 프리미티브가 전체 그룹을 나타낼 수 있으므로 약간의 정확도 손실로 메시 복잡성을 크게 줄일 수 있습니다. 원래 형상을 기반으로 등가 재료를 계산하여 정확도가 유지됩니다. 그림6은 via grouping 적용 전후 사진입니다.

[그림6] Via Grouping 적용 전/후

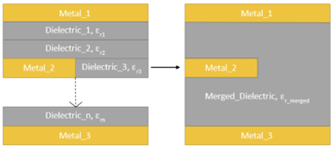

Dielectric Merging

반도체는 비슷한 전기적 특성을 지닌 여러 개의 얇은 필름이 적층되어 있기 때문에 각 층의 유전율 차이가 거의 없습니다. 따라서 각 층별로 메시를 자르면 전체 메시 수가 급격히 늘어나 컴퓨팅 리소스 소모가 늘어납니다. 이러한 문제를 해결하기 위해 HFSS에서는 유전 단순화 방법을 제공합니다.

이러한 방법은 각 층의 물리적 두께와 유전 상수를 결합하여 결합된 층의 등가 유전 상수를 계산합니다. 이 접근 방식의 이점은 합리적인 계산 정확도를 유지하면서 메시 요소 수를 줄여 계산 시간을 단축한다는 것입니다. 그림7은 Dielectric merging 전후 차이를 나타낸 그림입니다.

[그림7] Dielectric Merging 적용 전후

유전 단순화의 실제 적용을 위해 유사한 유전 특성을 가진 박막 레이어를 통합하면 메시의 복잡성을 크게 단순화하여 계산 효율성을 높일 수 있습니다. 이는 극도로 얇은 유전층을 많이 포함하는 반도체 설계에서 특히 중요합니다. 사용자 인터페이스 또는 FDB API를 통해 설계 요구 사항 및 계산 정확도 요구 사항을 기반으로 병합 및 단순화에 가장 적합한 방법을 선택할 수 있습니다.

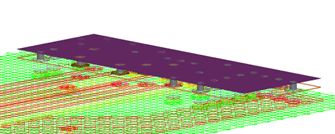

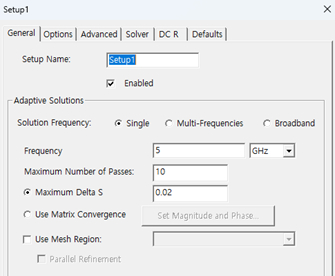

4. Excitations 및 Analysis Setup

앞의 과정으로 Interposer 모델링이 완료되면 해석 세팅을 합니다. Excitations 및 Analysis Setup을 해줍니다. Port 설정은 해당 Chip 위치에 Solder Ball 설정 후 원하는 Net에 지정합니다. Analysis Setup 설정에서 원하는 해석 주파수를 넣어주고 해석을 진행합니다. 그림8은 Solder ball 및 port 설정 사진입니다. 그림9는 analysis setup 설정 화면입니다.

[그림8] Solder Ball 및 Port 설정

[그림9] Analysis Setup 설정

5. Result 확인

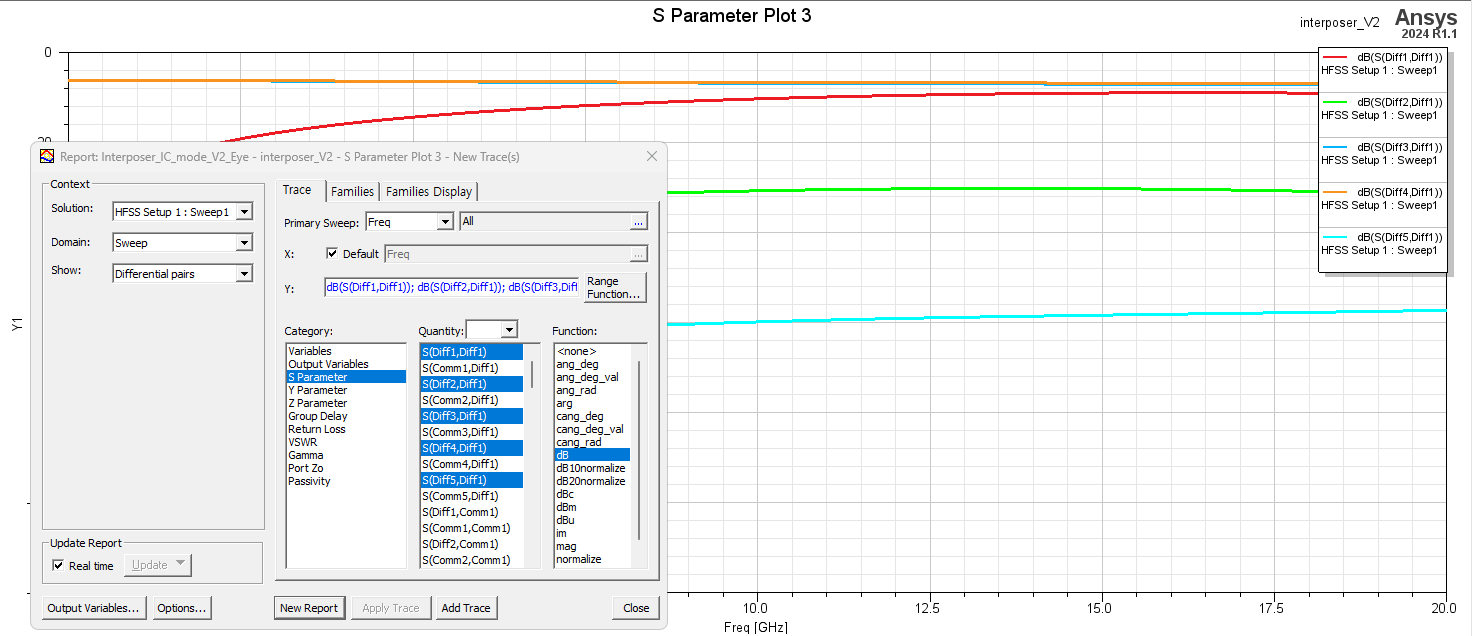

해석 완료 후에 Results 탭에서 S파라미터 결과를 확인할 수 있습니다. Single End 및 Differential Pair에 대한 결과를 확인할 수 있습니다. 그림10은 해석 결과 사진입니다.

[그림10] Differential pairs 설정 및 S파라미터 결과

맺음말

공학 시뮬레이션 분야의 선두주자인 ANSYS의 AEDT(ANSYS Electronics Desktop)는 HFSS, Icepak, RaptorX, Mechanical 등 다양한 물리 계산 엔진을 통합하여 업계에서 높은 평가를 받고 있습니다. 이러한 도구는 고주파 전자기장 시뮬레이션부터 열 분석, 구조 분석 및 신호 무결성 분석에 이르기까지 광범위한 솔루션을 제공하여 집적 회로(IC) 수준 전자 설계를 수행할 때 설계자의 분석 능력을 크게 향상시킵니다. 더 자세한 내용은 문의 주시면 도움 드리도록 하겠습니다.

㈜태성에스엔이

㈜태성에스엔이